Microelectronics Research Development Corporation

KM-803301; Temporal LatchTM SEU Immune RHBD 90nm CMOS 8 Bit RISC SoC

Electronic integrated circuits providing radiation hardening for digital logic architecture

Specifications:

8-Bit RISC CPU

Dual Voltage Supply 1.2V Core and 1.2V to 2.5V I/O

8-Bit RISC CPU

- 50 MHz Clock

- Based on Micro-RDC Enhanced Open Cores PIC

- Supports 2x96x8 Byte Register Files

- 8 bit GPIO

- Watch Dog Timer

- External Interrupt

- SEU Immune by Incorporating Temporal Latch Technology in all Sequential Logic

- On Chip Internal Register File (2x96x8)

- Temporal Latch Based Flip Flops

- On Chip 4Kx14bit EDAC Program RAM

- Bootup from External SPI EEPROM

- On Chip ROM for Testing and Bootup

- SPI Slave for Firmware Download and Upload to Silicon

- Support for 128 Kbytes External SPI Non Volatile Memory

- Dual I2C Bus

- I2C Master/Slave

- I2C Master

- SPI Master with Multiple Slave Chip Enables

- I2C Primary Master

- I2C Secondary Master

- I2C Slave

- SPI Master with 8 Slave Selects

- SPI Slave

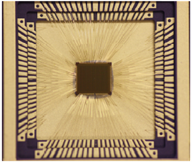

- 3.156mm X 3.543mm

- 172 Pins

- 96 CMOS I/O

- 64 um pad pitch

- 50 um X 50 um pad size

Dual Voltage Supply 1.2V Core and 1.2V to 2.5V I/O

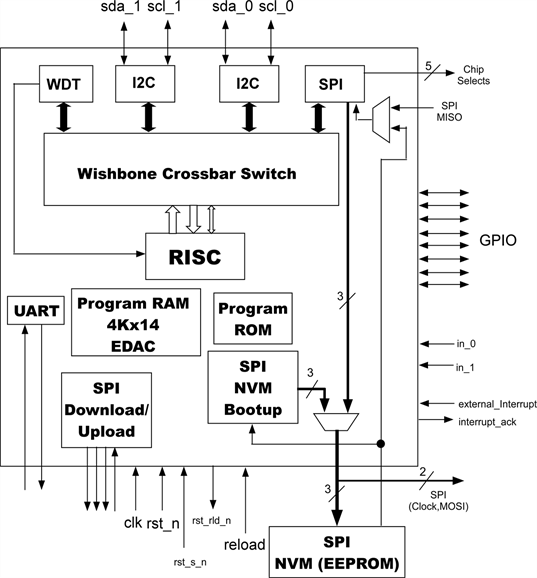

Block Diagram

RHBD IBM 9LP 90nm CMOS

- Total Ionizing Dose: Within specifications after exposure to greater than 1Mrad(Si)

- Single Event Latch Up: Latchup immune to 80 MeV-cm2/mg

- SRAM Error Rate: Supports scrubbing program SRAM to obtain desired error rates

- Single Event Transient: Implements the Temporal Latch-based flip flops to mitigate transient pulse widths of up to 1ns

KM-803301 Bondout 172 Pin CQFP Evaluation

This effort is sponsored by the Air Force Research Laboratory (AFRL).